お疲れ様です。

今回は素子の特性測定回路について書いていこうと思います。

もう1年ほど前になりますがmosfetのスイッチング特性を測定するための回路を設計製作していました。

mosfetの特性といっても実に様々な評価軸があり一概にコレという評価を付けるのが難しいのですが、素子の使われ方としてごく一般的なスイッチングにおける諸特性を測るのに便利な方法としてダブルパルス試験というものがあります。

ダブルパルス試験とはその名のごとくmosfetのGateに2回のパルスを入力してターンオン、ターンオフの過渡特性を測るものです。

■試験概要

・アイドリング電流

まず1回目のパルスをPulse1、2回目のパルスをPulse2と名付けます。(私ルール)

Pulse1のオン時間に従って回路に流れる電流は直線的に増加します。

その特性を利用し、ある電流が流れているときのmosfetのスイッチング特性を測定するためのパラメータとします。

上記試験概要では試験電流を10A、30A、60Aと設定していますが安全を考慮し、500mA、1A、1.5A~といった具合に少ない電流値からスタートする方がいいです。

で、実際の試験では数us程度の時間幅で変化させるためArduinoなどのus単位で変化させることのできる信号源を用意する必要があります。

ここで設定する試験電流が増えるに従い回路の振動が増えるため信号入力側と大電流側とでGNDを切り離しゲートの誤ターンオン・ターンオフを引き起こさないよう注意が必要です。

その他、電源に数千uF程度の水筒コンデンサを設置する必要があります。

大電流が流れた際の電源の振動を吸収するためには最低でもそのくらいの容量が必要になるからです。

後は配線のインダクタンス成分やインピーダンス成分も下げる必要があります。

回路の系で振動を引き起こす原因はインダクタンス成分です。

負荷にLを入れてますがその他の経路でも大電流が流れるため、如何に配線インダクタンスが低いとはいえ数十cmも引き延ばしているといけません。

また、細い線材を使っている場合最悪燃える可能性があるため必ず2sq以上はあった方がいいと思います。

上記のようなことに考慮しつつアイドリング電流の設定を行います。

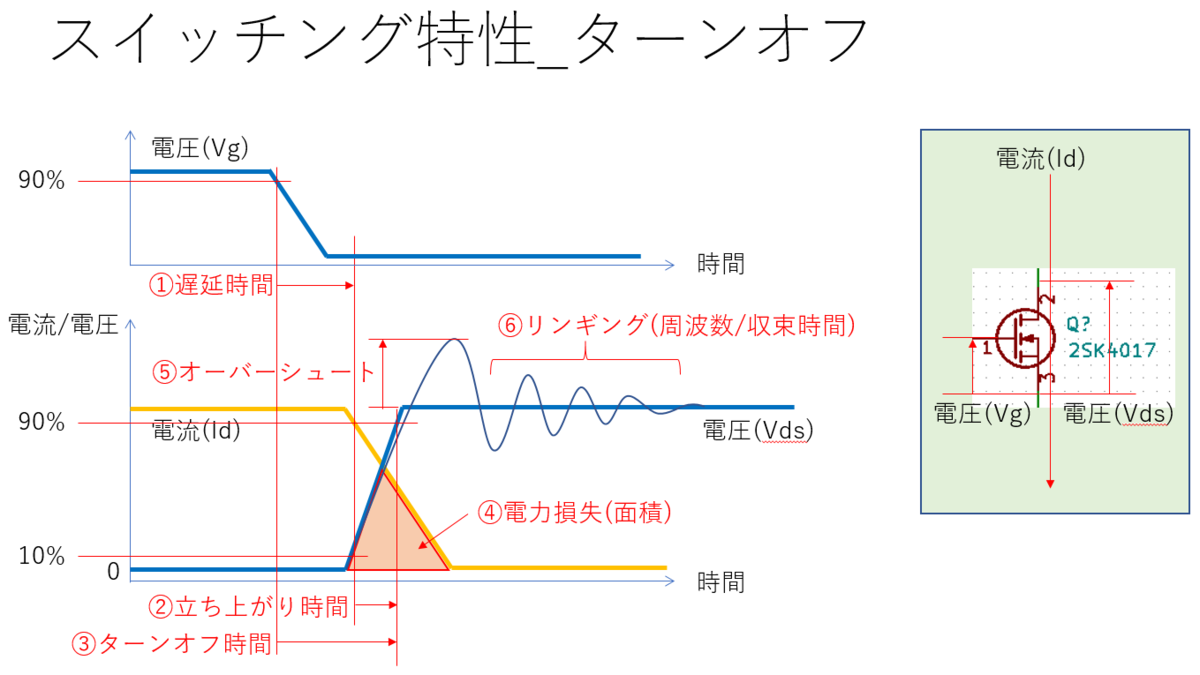

・ターンオフ特性

アイドリング電流の設定においてmosfetの遮断電流の設定を行ったら今度は実際にGateをオフしてDrain-Source間の電流を遮断します。

この時、mosfetの上流側には負荷を模擬したコイルが配置されています。

このコイルによって遮断しようとする動きに対して残留磁気による電流を流し続けようとする効果によって電源電圧よりも高い電圧が一瞬現れます。

これをオーバーシュートといいますが、これとともに目標の電圧値に収まるまでの振動も発生し、これをリンギングといいます。

このような背反をターンオフ特性として測定します。

・ターンオン特性

ターンオフ時のオーバーシュートと同様にアンダーシュートという現象がターンオン時にも発生します。

このような背反をターンオン特性として測定します。

・その他の特性

このほかにボディーダイオードの「逆回復特性」およびハイサイドNchの「誤ターンオン」なども測定における重要特性になりますが、試験回路構築においてそこまでの事ができておらずまず現状はスイッチング特性をうまく測れるようになることが重要だと思っています。

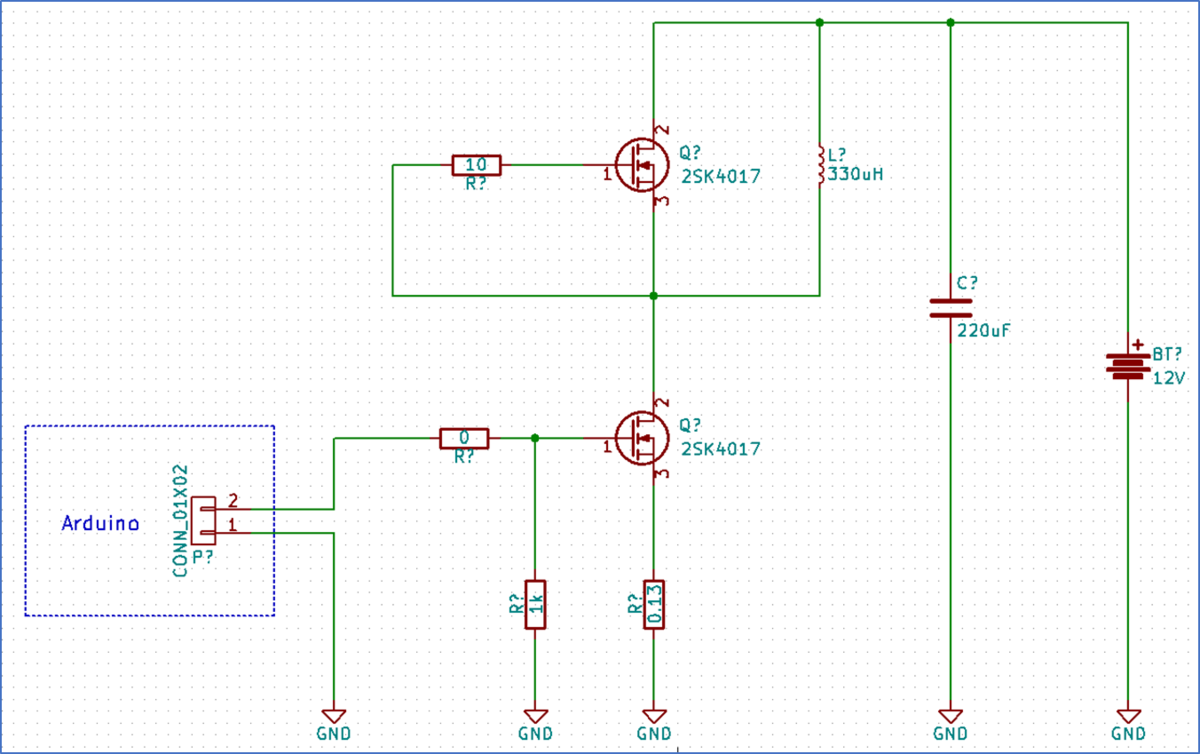

実際に作成した回路が上記写真になります。

モータードライブ用として一般的な2SK4017を試しに回路を構成してみました。

この測定は事前検討で行ったもので失敗に終わりましたが私と同じ足跡を辿る人がいるかもしれませんので間違った例として記事に起こしておきます。

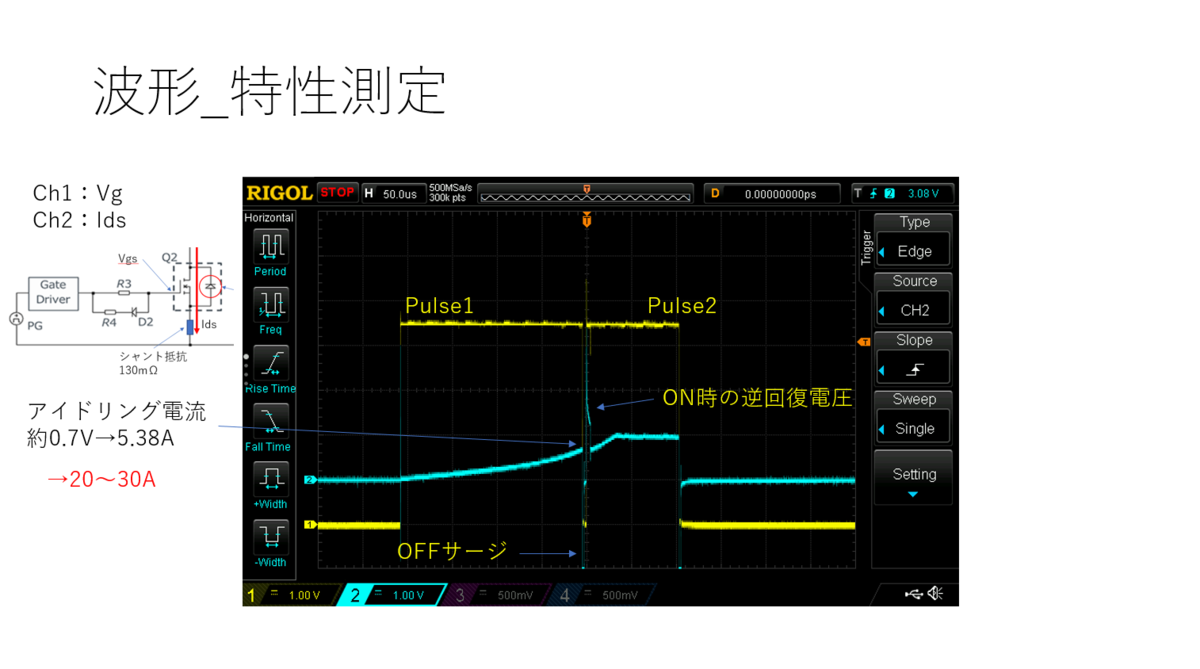

以下はその際の測定結果です。

測定結果1は全体波形で2がその拡大です。

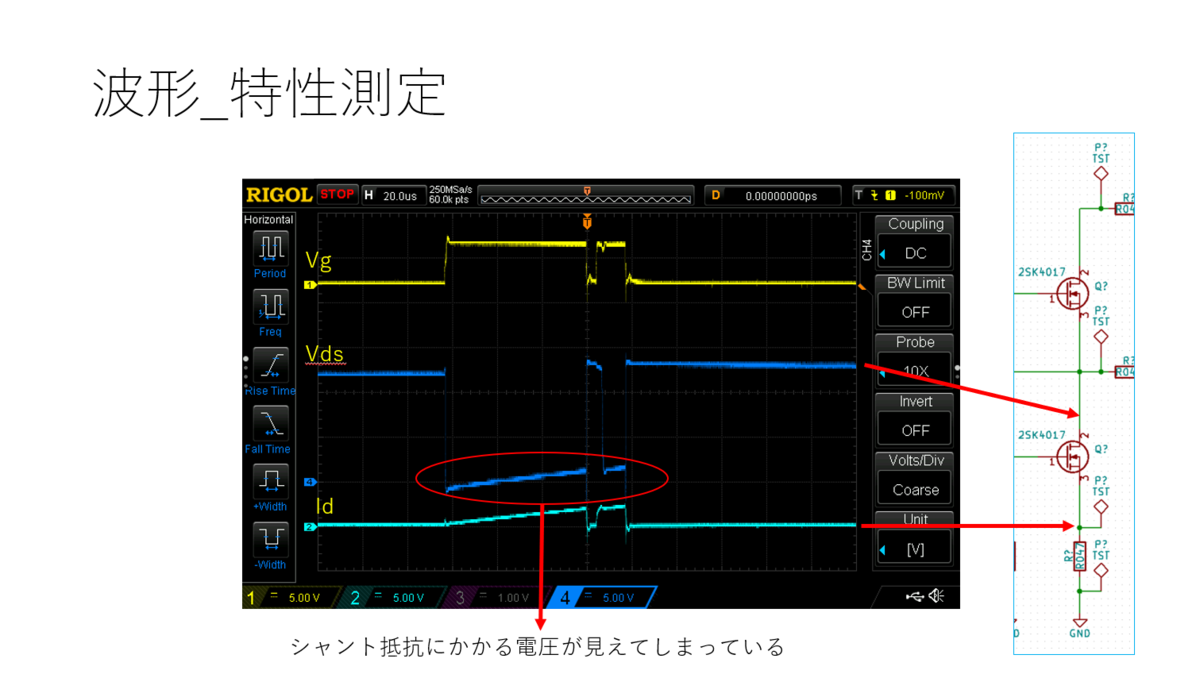

測定結果3は同じ回路で条件を変えて測定しなおしています。

この結果で問題となるのは電流の測定方法です。

値の不明瞭なシャント抵抗を用いたために回路に流れている本来の電流値を正確に測ることができていません。

また、測定結果3のように値の大きいシャント抵抗のためにmosfetのD-S間電圧に影響を及ぼしています。

実際にはもっと少ない電流が流れているのですがそれは後になって分かる話。

とりあえずそのあたりを考慮して再測定を実施した結果が下記になります。

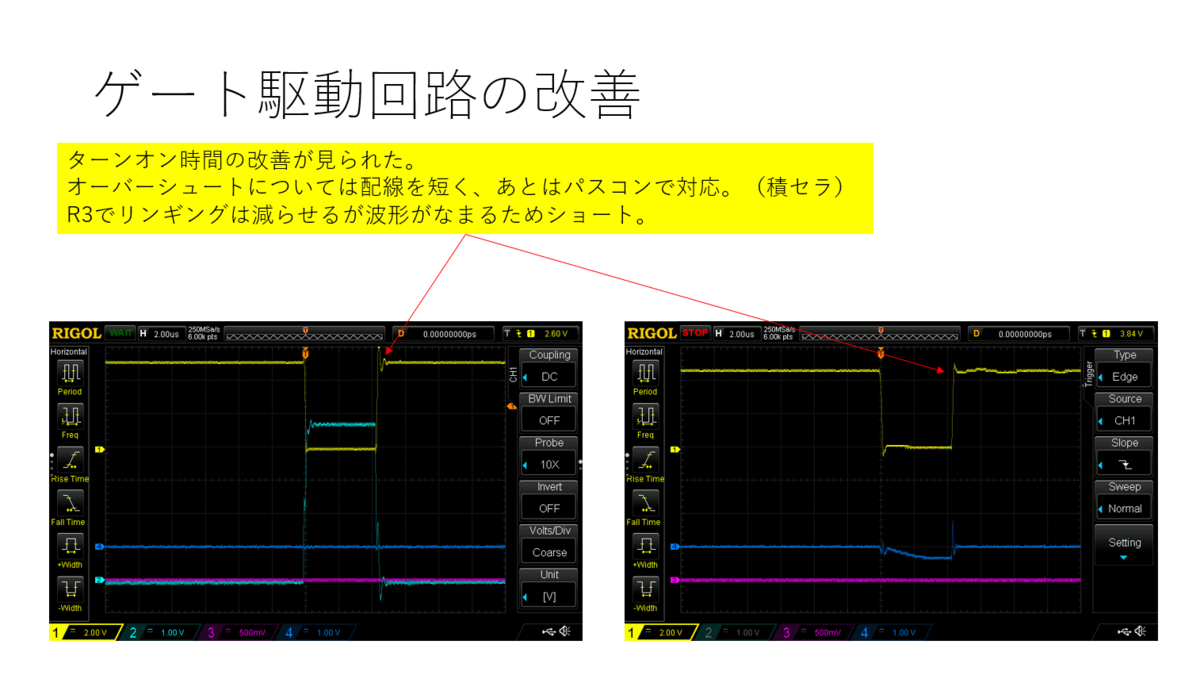

測定結果は画像のコメント通りなのですが、ここで注目すべきは結果4のゲート波形です。

これはmosfetを用いたスイッチングで必ず考慮しなければならない項目であると思いますが、Gate端子のCISS、いわゆる入力容量が影響してArduinoの出力端子で駆動しただけでは高速スイッチングできない(ドライブしきらない)問題が発生しているのです。

そのため、間にバッファを挟んで強力に充放電してやる必要があります。

その前提があって初めてmosfetのスイッチング特性が測定できます。

これは東芝のアプリケーションノートに記載されているシミュレーション結果とも一致しており、リンギングとの兼ね合いで直列接続の制限抵抗の値を決めますがGateドライブ回路がいかに複雑で難しいものであるかを物語っています。

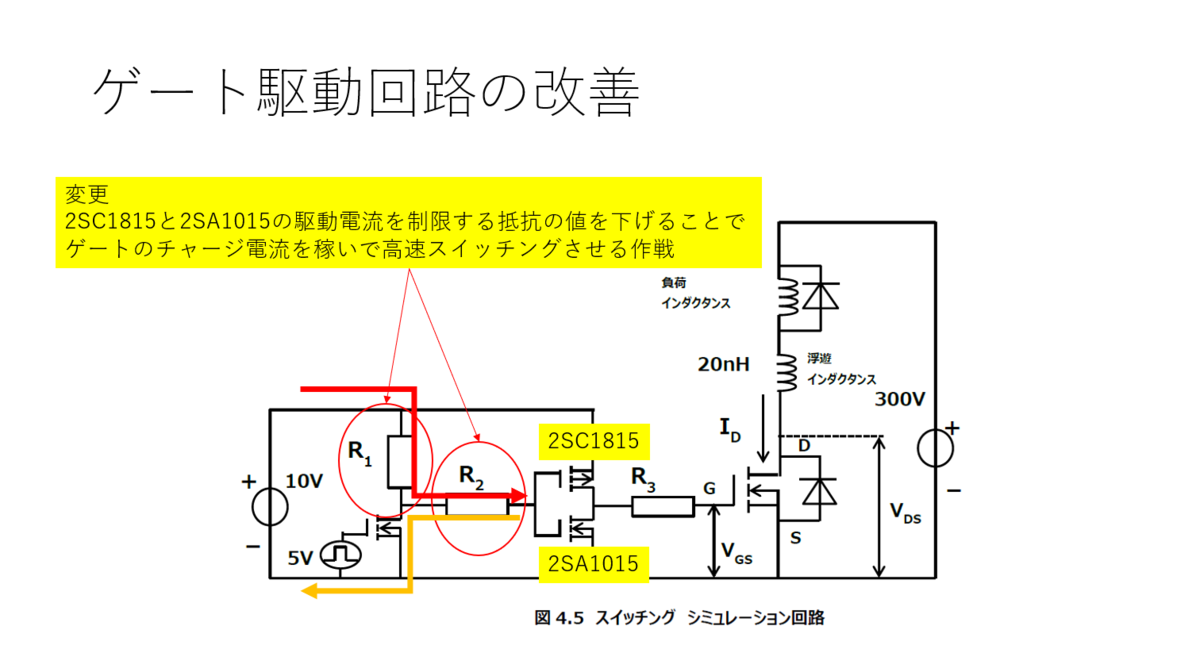

上記までの改善を色々と盛り込んで上記のような回路図が出来上がった。(2SA1943はエミッタ、コレクタが逆です。すみません。)

ターンオン、ターンオフのいずれでもゲート容量を駆動するためにはプッシュプル構成のトランジスタで駆動してやる必要があり、その信号波形もある程度強めに駆動する必要があるのとレベルシフトが必要なためmosfetでの駆動を間に挟む。

そうすることでターンオン、ターンオフの波形を瞬時に立ち上がり、立下りさせることができる。

ただしこれはゲート波形の改善をしたに過ぎず、メイン回路の負荷条件やコイルの定数などまだ考慮しなければならないことが残っている。

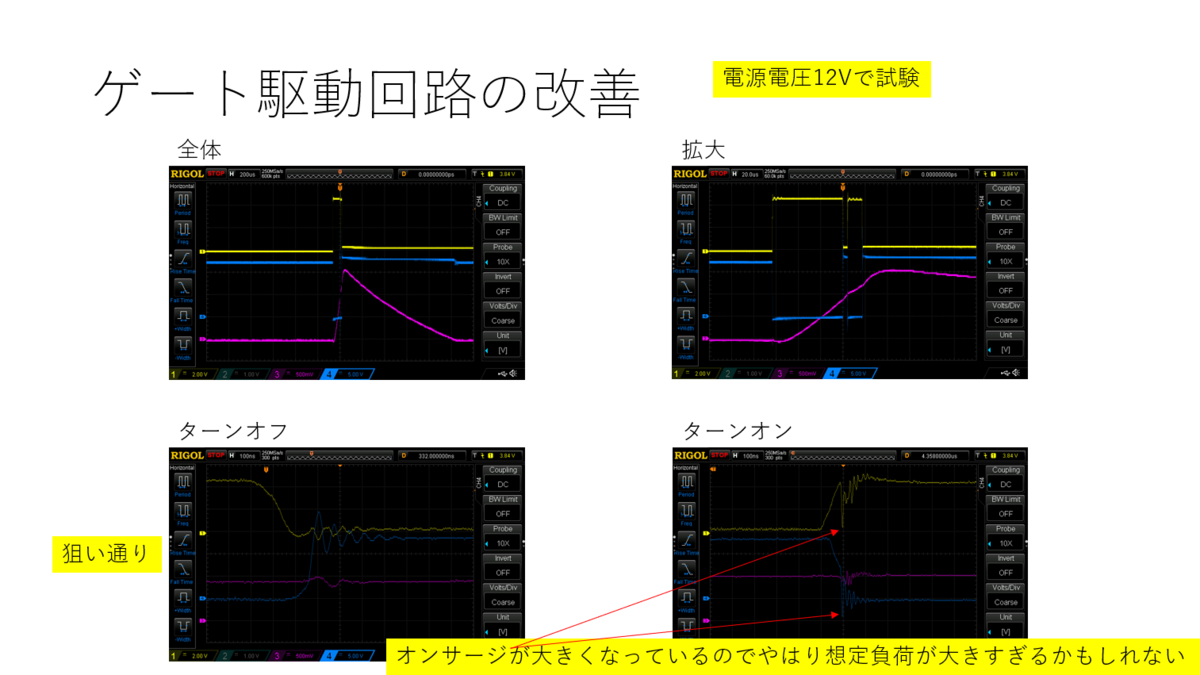

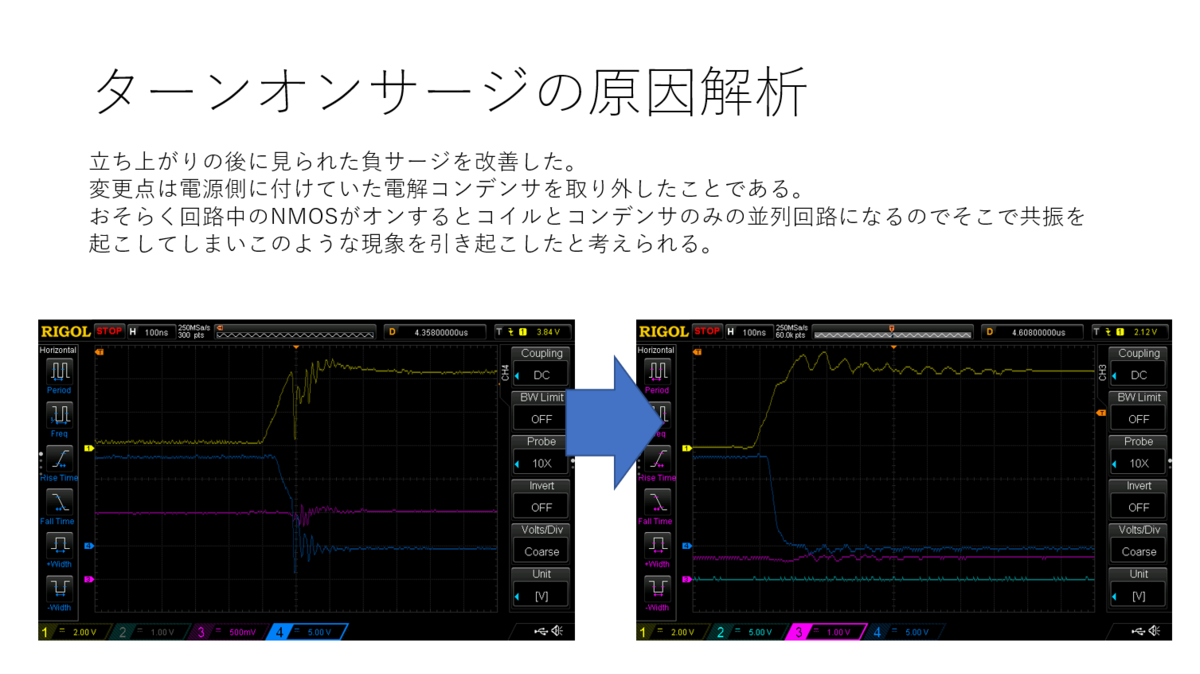

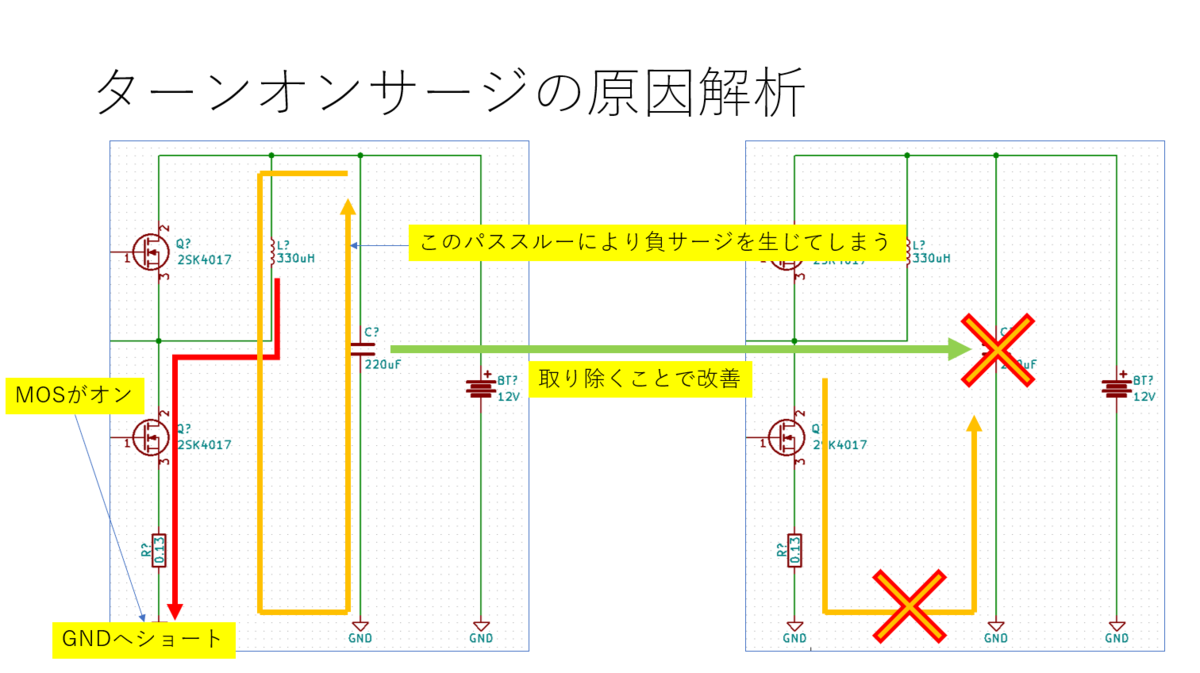

上記ではD-S間電圧波形に生じる立ち上がり直後のサージ対策について検証したものだ。

基本的に立ち上がりを急峻にしていくとアイドリング電流の量に従って回路全体の振動が増えてしまう。

それによる波形の乱れがひどく、見たい特性値の波形をうまく観測することが難しくなる。

それの対策、ないし測定回路の定数適正化として疑似負荷のコイル定数を見直した。

しかしながら色々と検証を重ねた結果コイル定数はアイドリング電流の立ち上がり時間を可変させるのみで、振動の主な原因はアイドリング電流値そのものであることが明らかとなった。

測定結果15で論じていることはおそらく正しいのだが、ここでやるべきことはコンデンサの削除ではなく定数の増加であった。

つまり、回路内の電流振動を抑え込むために必要なコンデンサ定数はもっと莫大にデカくなければならない。

経験しないとわからないが1000uF~4700uFくらいないと10~20Aもの電流の振動を抑え込むことができない。

通常の直流電源では数ns単位での電流変動に対して数Aもの電流のシンク・ソース出力などできない。

そこも見誤りやすい点である。

電流量が増えると電源の出力インピーダンスは意外に高くなってしまいがちということである。

これを回避できる電源があるとしたら所望の電流容量を有したプログラマブル電源などの4象限電源であろうと思うが高価でデカく重くなるし電源も100V駆動できなくなると思う。

従ってそこまでの大容量のコンデンサを積む必要があったということだ。

単にパワーのロマンに駆られているわけではない。

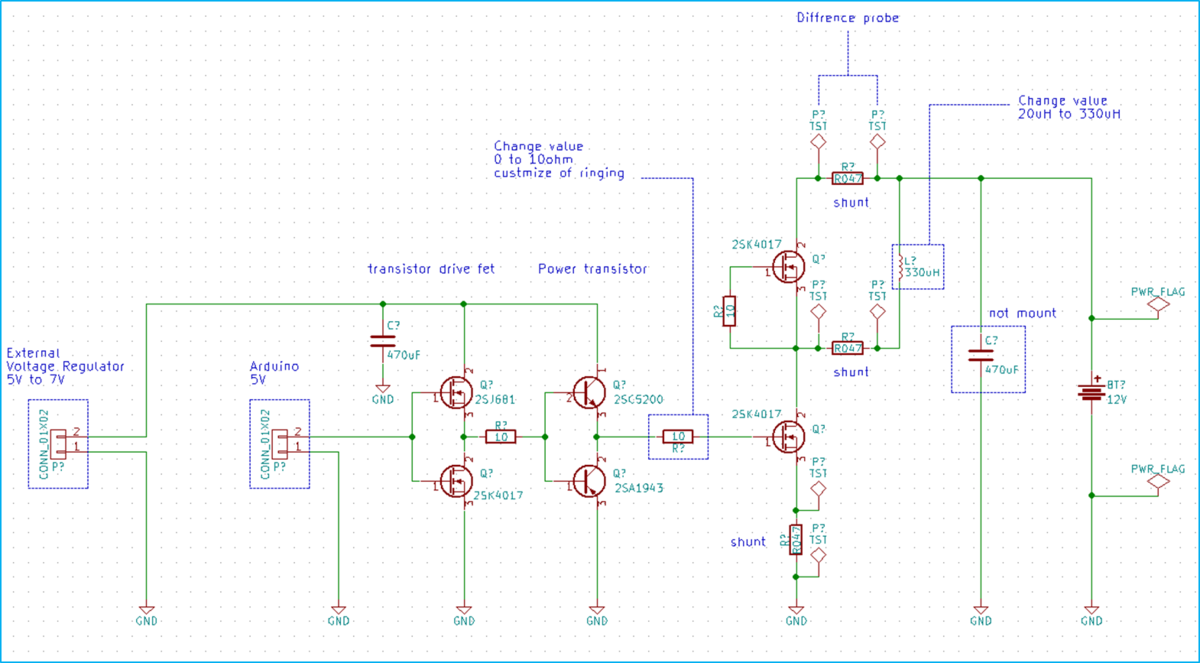

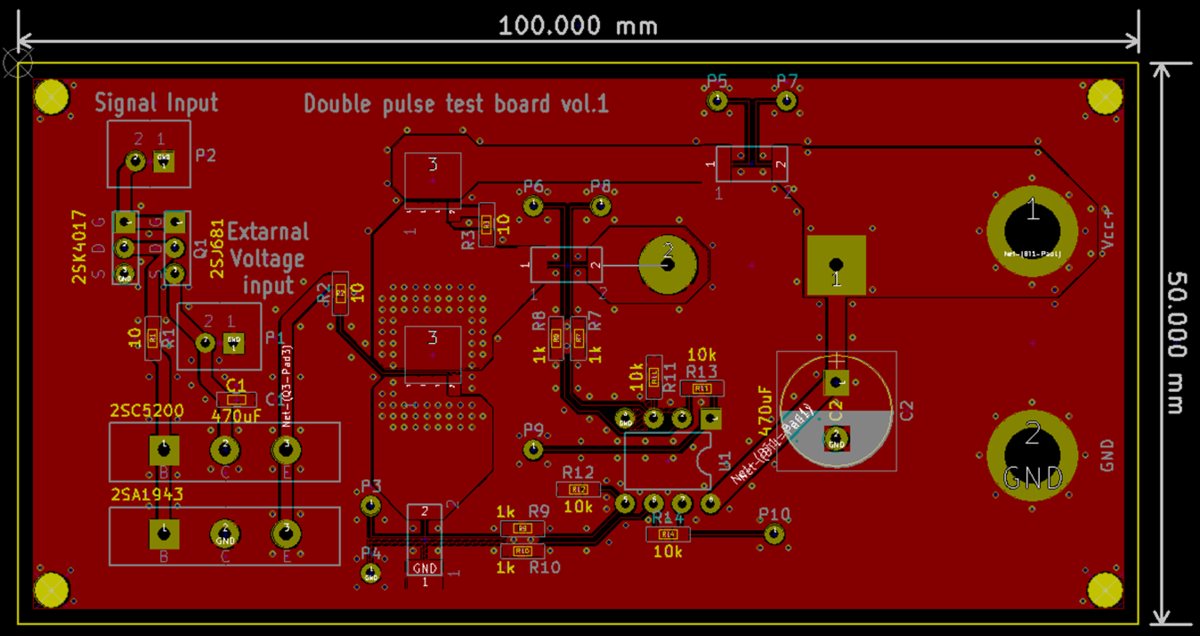

そういったわけでコンデンサを積むのと同時にセンシングアンプも付け足した回路の最終版が下記になる。

ここでまた間違いを犯している。

まずシングルエンドの入力なのだからハイサイドのシャント抵抗に対してOPアンプ一個では正確な差動信号を取り出すことは不可能である。

ここでやるべきは完全差動OPアンプを持ってきて差動入力を取るか、もしくはシャントのハイサイド側、ローサイド側をOPアンプ一個ずつ使って受けて、その出力を差動アンプで増幅してやる必要がある。

ただ、回路定数のマッチングがうまくいっていないとおかしなことになるので計装アンプや高精度抵抗と配線のインピーダンスなどを考慮した精密な設計が必要になるため、あまり現実的ではなく、あまり積極採用しない方が得策である。

どちらかというとオシロスコープの完全作動プローブを使って測定した方がいい。(やっていることは同じ。)

上記回路図をAWに書き出したのが下図。

この測定の完成を見るにはトランジスタ技術の特集によるのだが、それによって測定が完成し後に有名Youtuberのイチケンさんの動画でも取り上げられてよく知られるようになったと思う。

以上、このテーマで1年くらい悩み苦しんだ過程と結果を書きました。

疑問などあればコメントいただけますと幸いです。